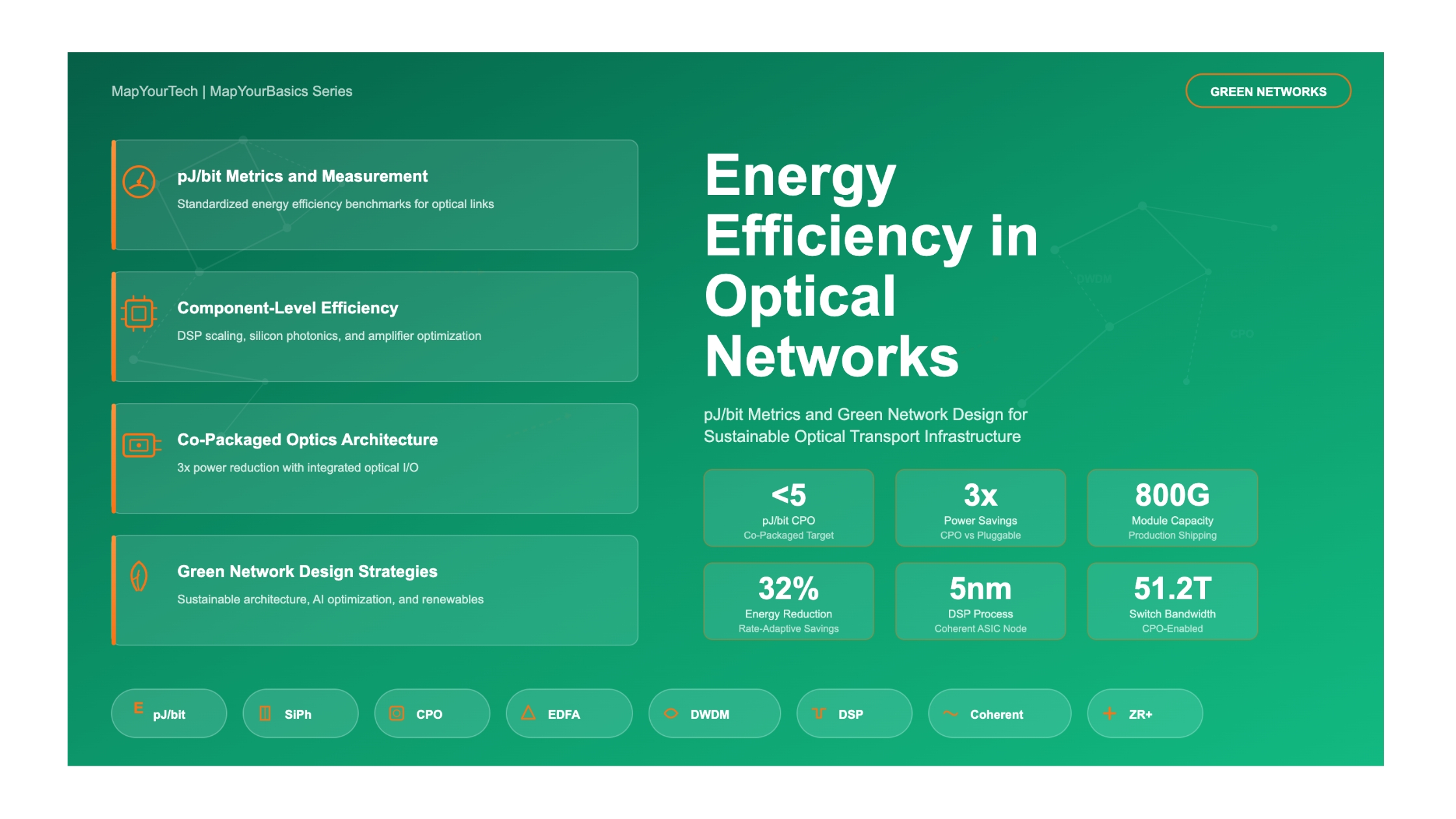

Energy Efficiency in Optical Networks: pJ/bit Metrics and Green Network Design

How the optical networking industry is measuring, optimizing, and transforming power consumption from component-level picojoules per bit to system-wide sustainable architecture

1. Introduction

The global Information and Communications Technology (ICT) sector consumes approximately 1,000 TWh of electricity annually as of 2023, accounting for roughly 1.8% to 3.9% of global greenhouse gas (GHG) emissions depending on the boundaries applied. Within this sector, optical transport networks form the backbone that carries over 95% of all inter-city and intercontinental data traffic. As bandwidth demand continues its exponential trajectory, driven by artificial intelligence workloads, cloud computing, and streaming media, the question of how much energy each transmitted bit costs has shifted from an operational footnote to a strategic priority for network operators, equipment vendors, and policymakers.

The metric at the heart of this transformation is picojoules per bit (pJ/bit), a measure of energy efficiency that quantifies the amount of energy consumed for every bit of data transported through a network element or across an end-to-end optical link. This seemingly simple number encapsulates the combined efficiency of lasers, modulators, Digital Signal Processors (DSPs), optical amplifiers, and cooling systems. As of 2026, the industry has fully embraced this shift: pJ/bit has superseded raw throughput (Gbps) as the primary Key Performance Indicator (KPI) for next-generation optical equipment, particularly in hyperscale data center environments where power budgets and thermal envelopes are the binding constraints on network scaling.

This article provides a comprehensive examination of energy efficiency in optical networks. It covers the fundamental physics behind pJ/bit calculations, traces the historical evolution of power consumption from 10G to 800G and beyond, analyzes the component-level and system-level strategies for reducing energy per bit, and examines emerging technologies such as co-packaged optics (CPO) and silicon photonics that promise to reshape the power landscape. The discussion bridges theory and practice, incorporating real-world deployment data, worked calculation examples, and forward-looking projections for green network design.

2. The Energy Challenge in Optical Transport

2.1 Scale of the Problem

Global IP traffic is projected to exceed 700 exabytes per month by 2027, with AI-related data center traffic growing at rates exceeding 40% per year. This traffic growth places enormous pressure on optical networks. A single hyperscale data center can consume 50 to 100 MW of electrical power, and a meaningful fraction, often 15% to 25%, is consumed directly by networking equipment including optical transceivers, switches, routers, and their associated cooling infrastructure.

Telecom network operators face a similar challenge. According to Ericsson's ICT sustainability research, the total ICT sector electricity consumption grew from 710 TWh in 2007 to approximately 1,000 TWh in 2023, and is estimated to have exceeded 1,050 TWh by 2025, even as the energy consumed per subscription and per gigabyte transported has decreased substantially. The challenge is clear: efficiency improvements are real and measurable, but aggregate traffic growth consistently outpaces efficiency gains, driving total power consumption upward.

Since 2007, the number of mobile and fixed subscriptions has grown 2.5 times and total data traffic has increased approximately 80 times. Yet total ICT electricity consumption grew only 1.4 times, demonstrating that substantial energy efficiency gains have already been achieved. The challenge is sustaining this rate of improvement as demand scales further.

2.2 Where the Energy Goes: Anatomy of an Optical Link

Continue Reading This Article

Sign in with a free account to unlock the full article and access the complete MapYourTech knowledge base.

Understanding energy efficiency in optical networks requires decomposing the end-to-end link into its constituent power consumers. Each component in the signal path draws power, and the relative contribution of each component varies significantly depending on whether the link is a 2-meter intra-rack connection or a 10,000 km submarine cable.

Figure 1: Power consumption breakdown of an end-to-end coherent optical link. The DSP and FEC processing dominate transceiver power, typically consuming 50-65% of total module power.

As Figure 1 illustrates, the DSP and Forward Error Correction (FEC) engine is the dominant power consumer within a coherent optical transceiver, accounting for 50% to 65% of total module power. This is followed by the data converters (DAC and ADC), the laser and its thermoelectric cooler (TEC), and the optical modulator driver. In the line system, optical amplifiers (EDFAs and Raman amplifiers) add significant power overhead, particularly in long-haul and submarine applications where dozens of amplifiers may be cascaded. Cooling overhead, expressed through the Power Usage Effectiveness (PUE) ratio, adds another 30% to 50% on top of the IT equipment power in a typical data center or central office.

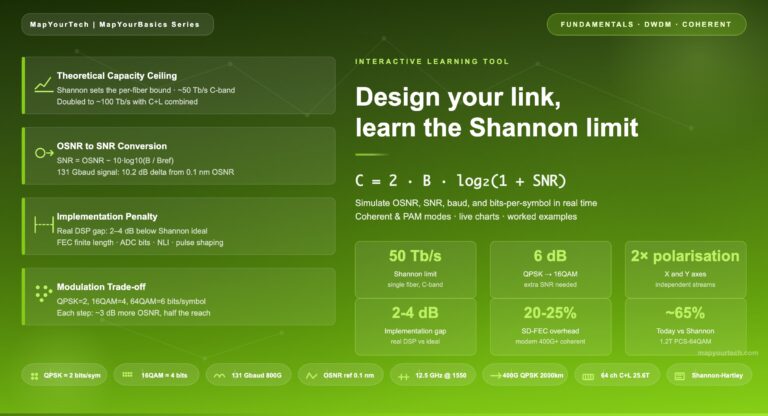

3. Understanding the pJ/bit Metric

3.1 Definition and Calculation

The picojoule per bit (pJ/bit) metric provides a standardized way to compare energy efficiency across different network elements, transceiver generations, and architectural approaches. One picojoule equals 10-12 joules. The fundamental relationship between power and energy per bit is straightforward.

Ebit = Ptotal / Rdata

Where:

Ebit = Energy per bit (pJ/bit)

Ptotal = Total power consumption of the element (watts)

Rdata = Aggregate data rate (bits per second)

-- Conversion note: 1 W / 1 Gbps = 1 nJ/bit = 1000 pJ/bit

-- Therefore: E_bit (pJ/bit) = P_total (mW) / R_data (Gbps)Worked Example: 400G ZR Transceiver

-- Given: A 400G ZR QSFP-DD module consuming 15 W

Ebit = Ptotal / Rdata

Ebit = 15 W / 400 Gbps

Ebit = 15,000 mW / 400 Gbps

Ebit = 37.5 pJ/bit

-- For comparison: A legacy 10G SFP+ at 1 W

Ebit = 1,000 mW / 10 Gbps = 100 pJ/bit

-- Improvement: 2.7x better energy efficiency at 400G vs 10G3.2 System-Level vs. Component-Level pJ/bit

A critical distinction exists between component-level and system-level pJ/bit. The transceiver module pJ/bit, as calculated above, captures only the energy consumed within the pluggable optic. The system-level metric must include the power consumed by switching ASICs, amplifiers along the optical path, control plane processing, and the cooling overhead for all of these elements. A 400G ZR module may deliver 37.5 pJ/bit at the transceiver level, but the system-level figure including the switch ASIC, SerDes, and cooling could easily be 100 to 200 pJ/bit for the complete port-to-port path.

When evaluating vendor claims about pJ/bit performance, engineers must always clarify the measurement boundary. The three common reference points are: (a) the optical engine or PIC only, which gives the most favorable number, (b) the full transceiver module including DSP, and (c) the system-level metric including the host electronics and cooling overhead. Each has its valid use cases, but direct comparisons require consistent boundaries.

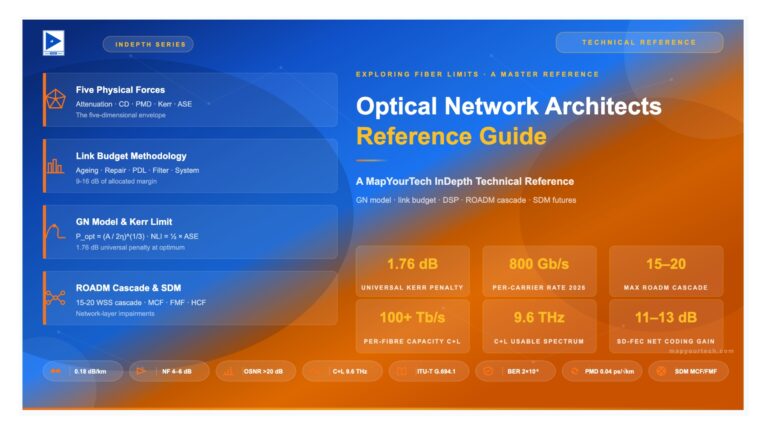

4. Historical Evolution of Optical Network Energy Efficiency

The optical networking industry has achieved remarkable improvements in energy efficiency over the past two decades. Each generation of transceiver technology has delivered higher capacity at progressively lower energy per bit, driven by advances in CMOS process technology, coherent DSP algorithms, photonic integration, and optical amplifier design.

The progression from 10G direct-detect transceivers to 800G coherent modules represents roughly a 10x improvement in energy efficiency per transported bit. Early 10G transceivers consumed approximately 80 to 100 pJ/bit. The introduction of 100G coherent systems using DP-QPSK modulation brought this down to 40 to 60 pJ/bit. As 200G and 400G systems adopted higher-order modulation formats and moved to more advanced CMOS nodes (from 40 nm to 16 nm and then to 7 nm), pJ/bit dropped to the 15 to 25 range. The current generation of 800G pluggable modules, built on 5 nm DSP processes, operates at 10 to 15 pJ/bit, with co-packaged optics (CPO) solutions in production demonstrating below 7 pJ/bit. First-generation 1.6T pluggables on 3 nm processes are beginning to ship in early 2026.

| Generation | Data Rate | DSP CMOS Node | Module Power (W) | pJ/bit (Module) | Modulation Format |

|---|---|---|---|---|---|

| 10G SFP+ | 10 Gbps | N/A (no DSP) | 0.8 - 1.0 | 80 - 100 | NRZ / OOK |

| 40G QSFP+ | 40 Gbps | N/A (no DSP) | 2.5 - 3.5 | 63 - 88 | 4x10G NRZ |

| 100G CFP / CFP2 | 100 Gbps | 40 nm | 6 - 20 | 60 - 200 | DP-QPSK |

| 100G QSFP28 | 100 Gbps | N/A (PAM4) | 3.0 - 4.5 | 30 - 45 | 4x25G NRZ/PAM4 |

| 200G / 400G CFP2-DCO | 200-400 Gbps | 16 nm | 12 - 18 | 30 - 60 | DP-16QAM |

| 400G ZR / ZR+ (QSFP-DD) | 400 Gbps | 7 nm | 14 - 18 | 35 - 45 | DP-16QAM |

| 800G OSFP/QSFP-DD | 800 Gbps | 5 nm | 15 - 25 | 19 - 31 | DP-16QAM / DP-64QAM |

| 1.6T (Early Production) | 1,600 Gbps | 3 nm / 2 nm | 20 - 28 | 12 - 18 | DP-64QAM / DP-256QAM |

| CPO Optical I/O | 800G - 4 Tbps | 3 nm co-packaged | 5 - 12 | 3 - 7 | PAM4 / Coherent Lite |

The most transformative efficiency gains have consistently come from two sources: (1) migrating the DSP ASIC to smaller CMOS process nodes, which reduces the power of digital logic roughly in proportion to the square of the voltage reduction, and (2) increasing the data rate per transceiver, which amortizes the fixed overhead power (laser, TEC, packaging) across more bits. A 400G transceiver operating at 64 Gbaud with DP-16QAM consumes approximately 2.5 watts per gigabit, while a legacy 100G transceiver at 32 Gbaud with DP-QPSK consumes about 4 watts per gigabit.

5. Component-Level Strategies for Reducing pJ/bit

5.1 DSP and CMOS Process Advancement

The DSP is the single largest power consumer in a coherent transceiver, and its efficiency is directly tied to the CMOS process node. Each major node transition, from 16 nm to 7 nm to 5 nm and now to 3 nm, reduces the dynamic power of the digital logic by roughly 30% to 50%. This reduction stems from lower supply voltages and smaller transistor capacitances. As of 2026, leading coherent DSPs for 800G applications are manufactured on 5 nm CMOS processes, with 3 nm designs now entering volume production for 1.6T systems. The industry target is to reach DSP power levels below 5 to 6 pJ/bit at the module level by 2029-2030, which will require DSPs on 2 nm processes combined with algorithmic optimizations.

Algorithmic improvements also play a role. More efficient FEC coding schemes, reduced-complexity equalization algorithms, and machine learning-based approaches to carrier recovery and nonlinearity compensation can reduce the number of operations per bit, translating to lower DSP power at the same process node. Research from rate-adaptable optical transmission demonstrates that DSP power consumption scales linearly with the clock rate, showing a 41% reduction in power between the highest and lowest investigated bit rates in FPGA-based implementations.

5.2 Photonic Integration and Silicon Photonics

Photonic Integrated Circuits (PICs) dramatically reduce the size, power consumption, and cost of optical front-end components. Three primary integration technologies are in active development and production.

InP PICs can monolithically integrate lasers, modulators, and photodetectors on a single chip. They offer the advantage of native laser integration but face challenges in yield and cost at scale. InP remains strong for high-performance coherent applications where laser quality is critical.

SiPh uses CMOS-compatible fabrication processes, enabling large wafer sizes, high yield, and low cost. As of 2026, annual shipments of SiPh-based 800G modules have surpassed 7 million units globally. Intel, Cisco, and others have demonstrated hybrid laser-on-wafer integration to address the missing laser challenge on silicon. Roughly 44% of optical transceivers are projected to use silicon photonics by 2028, up from 24% in 2022.

Planar Lightwave Circuit (PLC) hybrids co-package silica-based waveguides with III-V photodetectors and LiNbO3 modulators. They offer the best raw optical performance but with lower monolithic integration levels. PLC hybrids remain relevant for ultra-high-performance coherent receivers.

Silicon photonics has achieved significant power advantages through tight integration. By placing modulators, photodetectors, and polarization handling elements on a single silicon die, SiPh eliminates discrete component interconnections and their associated losses. Low-voltage silicon Mach-Zehnder modulators (MZMs) and microring modulators have demonstrated drive powers well below 1 pJ/bit for the optical modulation function alone. A 2024 demonstration of a CMOS-integrated silicon photonics transmitter achieved 112 Gbaud operation at 0.7 pJ/bit energy efficiency by using a switching-current drive approach rather than traditional voltage-swing drive.

5.3 Optical Amplifier Efficiency

Erbium-Doped Fiber Amplifiers (EDFAs) are used extensively in long-haul and metro DWDM networks. A typical EDFA provides 20 to 30 dB of gain with a noise figure of 4 to 6 dB. Pump power typically ranges from 200 mW to 1 W for C-band EDFAs, with total module power consumption of 10 to 25 W including control electronics and thermoelectric stabilization. Key efficiency improvements include higher wall-plug efficiency pump lasers (now exceeding 50% electrical-to-optical conversion), optimized erbium fiber lengths, and counter-directional pumping architectures that reduce the total pump power required for a given gain.

Hybrid Raman-EDFA configurations provide a further 3 to 5 dB improvement in noise figure compared to standalone EDFAs, enabling wider span spacing and fewer amplifiers for a given link length. This translates directly to lower total system power per transported bit on long-haul routes.

5.4 Rate-Adaptive Transmission

Elastic Optical Networks (EONs) use rate-adaptive transceivers that can adjust their data rate to match actual traffic demand. This capability enables two energy-saving approaches: modulation format adaptation, where the transceiver switches between QPSK, 8QAM, and 16QAM depending on the required reach and capacity, and symbol rate adaptation, where the baud rate is reduced during low-traffic periods. Research shows that symbol rate adaptation reduces DSP power roughly in proportion to the clock frequency, with measured reductions of up to 41% when lowering the rate from 30 Gbps to 7 Gbps. In European-scale network studies, following daily traffic variations with combined modulation and symbol rate adaptation delivered up to 32% energy savings.

6. System-Level Green Network Design

6.1 Co-Packaged Optics (CPO): A Transformational Approach

Co-packaged optics represents the most significant architectural shift in optical interconnect design for data centers. By integrating optical engines directly onto the same substrate as the switch or compute ASIC, CPO eliminates the long electrical traces between the ASIC and front-panel pluggable transceivers. This reduces SerDes power, removes the need for retimer ICs, and shortens the electrical path from centimeters to millimeters.

Figure 3: Comparison of traditional pluggable and co-packaged optics architectures showing the 3x improvement in energy per bit.

As of 2026, several major CPO developments have validated this approach. Broadcom's Bailly chip integrates 6.4 Tbps silicon photonics optical engines inside the ASIC package, achieving approximately 5.5 W per 800 Gbps port, which translates to 6 to 7 pJ/bit. NVIDIA's Spectrum-X and Quantum-X photonic switches, first unveiled at GTC 2025 and now entering broader deployment, scale to over 100 Tbps. Intel's Optical Compute Interconnect (OCI) chiplet prototype demonstrated 4 Tbps bidirectional throughput at approximately 5 pJ/bit, compared to about 15 pJ/bit for pluggable modules. For a fully loaded 64-port (800G each) switch, the CPO approach saves hundreds of watts compared to an equivalent pluggable design.

6.2 Power-Aware Network Planning

Beyond component-level improvements, system architects can reduce total energy consumption through intelligent network design choices. These include optimizing amplifier placement to minimize the total number of EDFA sites along a route, selecting modulation formats that balance spectral efficiency against DSP power (lower-order formats like QPSK consume less DSP power per bit than 64QAM, though they require more fiber bandwidth), and engineering the optical layer to maximize transparent reach, thereby avoiding power-hungry optical-electrical-optical (OEO) regeneration nodes.

IP-over-DWDM architectures, where the router or switch interfaces directly with coherent DWDM wavelengths without intermediate transponder shelves, eliminate an entire layer of equipment and its associated power consumption. The growth of 400G ZR and ZR+ pluggable coherent optics has made this approach practical for metro and regional networks, enabling operators to reduce both equipment count and per-bit energy consumption.

6.3 AI-Driven Energy Optimization

Machine learning algorithms are increasingly used to optimize energy consumption across optical networks in real time. These systems can dynamically adjust modulation format and launch power of coherent transceivers based on measured channel conditions, predict traffic patterns to pre-emptively power down unused ports and amplifiers during low-demand periods, and optimize wavelength routing to consolidate traffic onto fewer active amplifiers. Network trials have demonstrated 20% or greater energy savings through AI-based traffic engineering and dynamic power management, with no degradation in service quality.

7. Power Consumption Across Network Segments

Energy efficiency requirements and solutions vary significantly across different optical network segments. Each segment has distinct distance, capacity, and operational constraints that shape the power consumption profile.

7.1 Data Center Interconnect (DCI)

DCI links, typically spanning 2 to 120 km between data center facilities within a metro area, represent the highest-volume and fastest-growing optical interconnect market. Power efficiency is the primary procurement driver in this segment, surpassing upfront cost for most hyperscale operators since 2025. A typical 400G QSFP-DD ZR module for 80 km DCI consumes 14 to 18 W, delivering approximately 35 to 45 pJ/bit. The transition to 800G and CPO architectures is well underway, bringing this below 10 pJ/bit in production deployments.

A major US cloud provider that deployed 50,000 units of 400G QSFP-DD modules for AI cluster expansion reported a 25% reduction in network power consumption compared to the previous 200G infrastructure, while doubling the effective bandwidth per rack unit. This demonstrates that capacity upgrades can simultaneously improve both throughput and energy efficiency.

7.2 Metro and Regional Networks

Metro networks span 80 to 600 km and typically use 100G to 400G coherent transmission. Power consumption in this segment is dominated by the transceiver modules at each endpoint and the EDFA amplifier chain along the route. A metro network using DP-16QAM modulation typically achieves approximately 0.5 watts per gigabit, while long-haul networks using DP-QPSK consume about 1 watt per gigabit due to additional amplification and regeneration requirements.

7.3 Long-Haul and Submarine

Long-haul networks (600 to 6,000 km) and submarine cables (up to 15,000 km) have the most constrained power budgets. In submarine systems, the total electrical power available for the entire repeater chain is delivered through the cable itself, with typical power feed voltages of 10 to 15 kV and total repeater chain power budgets of 10 to 20 kW for systems spanning thousands of kilometers. Each inline EDFA in a submarine system consumes 10 to 20 W, and the system may contain hundreds of amplifiers. Lower-order modulation formats (BPSK and QPSK) are used because they require less OSNR and therefore fewer amplifiers per span, even though they provide less capacity per wavelength. The energy per bit in submarine systems is significantly higher than in DCI, often reaching hundreds of pJ/bit when the entire amplifier chain power is factored in.

| Segment | Typical Distance | Dominant Data Rate | Key Power Consumers | System pJ/bit Range |

|---|---|---|---|---|

| Intra-DC (short-reach) | 0.5 - 2 km | 400G - 800G | Transceiver (PAM4, no DSP) | 5 - 25 |

| DCI (campus) | 2 - 10 km | 400G - 800G | Transceiver + switch ASIC | 15 - 50 |

| DCI (metro) | 10 - 120 km | 400G ZR/ZR+ | Coherent DSP + amplifiers | 35 - 80 |

| Metro / Regional | 120 - 600 km | 200G - 400G | DSP + EDFA chain + ROADM | 60 - 200 |

| Long-Haul | 600 - 6,000 km | 100G - 400G | EDFA chain dominates | 100 - 500 |

| Submarine | 3,000 - 15,000 km | 100G - 200G | Repeater chain + power feed | 200 - 1000+ |

8. Green Network Design Strategies and Best Practices

8.1 Network Architecture Optimization

Green network design starts at the architectural level. Key strategies include minimizing OEO conversions by maximizing transparent optical reach using advanced amplification and coherent DSP; using IP-over-DWDM to eliminate intermediate transponder shelves; deploying flex-grid ROADMs with fine channel spacing (e.g., 37.5 GHz or flexible grids) to maximize spectral utilization per watt of amplifier power; and planning fiber routes to minimize the number of amplifier huts while maintaining adequate OSNR margins.

8.2 Traffic-Responsive Power Management

Networks experience significant traffic variation across the day, with peak-to-trough ratios of 3:1 or higher in many metro and core networks. A fixed-power network wastes substantial energy during off-peak hours. Traffic-responsive strategies include putting unused transponder ports into low-power sleep states, reducing baud rates on active channels during low-traffic periods to save DSP power, consolidating traffic onto fewer active wavelengths and powering down unused amplifiers, and using dynamic voltage and frequency scaling (DVFS) on DSP ASICs.

European network simulation studies have shown that implementing both modulation format and symbol rate adaptation in response to daily traffic variations can deliver up to 32% energy savings in core networks. Additional savings of up to 20% are achievable by placing spare protection resources in low-power standby mode until needed for fault recovery.

8.3 Renewable Energy and Sustainability Integration

Optical network infrastructure is increasingly powered by renewable energy sources. Major hyperscale operators have committed to powering their data centers with 100% renewable energy, and many telecom operators have set similar targets for their network infrastructure. Google's 24/7 Carbon-Free Energy (CFE) goal represents one of the most ambitious initiatives, aiming to match every unit of electricity consumed with carbon-free energy on an hourly basis. The optical transport network plays a direct role in this by connecting renewable-powered data centers and by reducing the total energy demand through the efficiency improvements described throughout this article.

A telecom operator upgraded its metro network from 100G DP-QPSK transceivers (32 Gbaud, ~20 W each) to 400G DP-16QAM transceivers (64 Gbaud, ~16 W each on 7 nm DSP). The results:

Before: 40 x 100G links = 4 Tbps capacity, 40 x 20 W = 800 W transceiver power, energy efficiency = 200 pJ/bit (system-level with amplifiers)

After: 10 x 400G links = 4 Tbps capacity, 10 x 16 W = 160 W transceiver power, energy efficiency = 80 pJ/bit (system-level with amplifiers)

Savings: 80% reduction in transceiver power (800 W to 160 W), 60% reduction in system pJ/bit, 75% fewer amplifier channels required, reduced cooling load equivalent to an additional 200 W savings.

9. Emerging Technologies and Future Directions

9.1 Linear-Drive Pluggable Optics (LPO)

Linear-drive pluggable optics (LPO), also known as Linear Receive Optics (LRO), is an intermediate approach between traditional DSP-based pluggables and CPO. LPO removes the DSP retimer from the pluggable module, instead relying on the host ASIC's SerDes to handle equalization directly. This eliminates 2 to 5 W of retimer power per port and reduces latency. LPO began shipping in NVIDIA Spectrum-X and Meta AI networks in 2025, and by early 2026 it covers an estimated 40% or more of short-reach 800G links in AI data centers, with rapid growth continuing as 1.6T deployments ramp.

9.2 Space-Division Multiplexing (SDM)

Space-Division Multiplexing uses multi-core fibers (MCF) or few-mode fibers (FMF) to multiply the capacity of a single fiber strand by a factor of 4 to 30. From an energy perspective, SDM enables capacity scaling without proportional increases in the number of amplifiers and transceivers. By consolidating multiple spatial channels into a single fiber, SDM reduces the energy consumption and hardware required to manage multiple parallel fiber systems. Research demonstrations have achieved over 1 petabit per second total capacity through multi-core fiber with 10 spatial channels.

9.3 Optical Switching and Photonic Computing

All-optical switching using reconfigurable optical add-drop multiplexers (ROADMs) and wavelength-selective switches (WSS) already eliminates OEO conversion at intermediate nodes. Future advances in optical circuit switching and photonic tensor processing could further reduce the electronic processing power by performing certain network functions directly in the optical domain. Companies like Lightmatter are developing silicon photonics interposers designed to optically connect AI accelerator chips, potentially eliminating electronic switching entirely for certain data movement patterns within AI clusters.

9.4 Industry Roadmap: pJ/bit Targets

The industry consensus target is to reach 5 to 6 pJ/bit for pluggable transceivers by approximately 2029 to 2030, enabled by 2 nm DSP processes, improved laser and modulator efficiency, and reduced coupling losses. CPO architectures aim for below 3 pJ/bit in the same timeframe. These targets are critical for ensuring that optical networking can scale to meet AI-era bandwidth demands without overwhelming data center power budgets and grid infrastructure.

10. Practical Design Guidelines for Energy-Efficient Optical Networks

Network architects and engineers can apply several practical principles to minimize energy per bit in their optical network designs. These guidelines span component selection, system configuration, and operational practices.

First, always select the highest-capacity transceiver that the link budget supports. A single 400G transceiver is always more energy-efficient per bit than four 100G transceivers, even if the total power consumption is similar, because the overhead power (laser, TEC, packaging, and cooling) is amortized over four times the data rate. Second, specify the latest DSP generation available. The difference between a 16 nm and a 5 nm coherent DSP can be a 3x improvement in energy efficiency for the same line rate. Third, match the modulation format to the application: use QPSK for long-haul where reach matters and 16QAM or 64QAM for metro/DCI where capacity density is the priority. Fourth, wherever possible, eliminate OEO conversion points by maximizing transparent reach with appropriate amplification and FEC coding gain. Fifth, implement traffic-responsive power management to reduce energy during off-peak periods. Sixth, evaluate CPO and LPO architectures for new data center builds where the power savings justify the change in operational model (CPO modules are typically not field-replaceable like pluggable transceivers).

Esystem = (PTx + PRx + Namp x Pamp + PROADM + Pswitch) x PUE / Rdata

Where:

PTx = Transmitter module power (W)

PRx = Receiver module power (W)

Namp = Number of inline amplifiers on the path

Pamp = Power per amplifier (W) — typically 15-25 W for EDFA

PROADM = ROADM node power allocated to this channel (W)

Pswitch = Switch ASIC power allocated to this port (W)

PUE = Power Usage Effectiveness (typically 1.3 to 1.5)

Rdata = Data rate in bits per second

-- Example: 400G ZR link, 80 km, 1 EDFA, no ROADM

Esystem = (8 + 8 + 1 x 20 + 0 + 5) x 1.4 / 400e9

Esystem = 41 x 1.4 / 400e9 = 57.4 W / 400 Gbps

Esystem = 143.5 pJ/bit (system-level with cooling)- pJ/bit is replacing Gbps as the primary KPI for optical network equipment in data center and AI infrastructure, with CPO achieving 5 to 7 pJ/bit versus 15 pJ/bit for pluggable transceivers.

- DSP power dominates coherent transceiver energy consumption (50-65% of module power), making CMOS process advancement the single most impactful lever for reducing pJ/bit.

- Co-packaged optics delivers a 3x improvement in energy efficiency by eliminating retimer ICs and minimizing electrical interconnect losses between the ASIC and optical engine.

- System-level energy efficiency depends on the complete signal path including amplifiers, ROADM nodes, switch ASICs, and cooling overhead (PUE), and must always be calculated at consistent boundaries when comparing solutions.

- Elastic/rate-adaptive transmission, AI-driven power management, and traffic-responsive network operation can deliver 20% to 32% additional energy savings beyond hardware improvements alone.

11. Conclusion

Energy efficiency has moved from a secondary concern to the defining design constraint for next-generation optical networks. The pJ/bit metric provides a rigorous, universally applicable framework for measuring and comparing the energy cost of transporting data across any optical link, from a 2-meter intra-rack connection to a transoceanic submarine cable. The industry has already achieved remarkable progress: a roughly 10x improvement in transceiver-level pJ/bit from the 10G era (100 pJ/bit) to today's 800G CPO solutions (5 to 7 pJ/bit), driven by CMOS process scaling, photonic integration, and coherent DSP innovation.

The path forward is clear but demanding. Reaching the industry's target of below 5 pJ/bit for pluggable modules and below 3 pJ/bit for co-packaged optics will require continued CMOS scaling to 2 nm and beyond, widespread adoption of silicon photonics with integrated lasers, intelligent network-level power management using AI, and new architectural approaches including space-division multiplexing and optical switching. For network operators, the practical implication is that energy efficiency must become a first-order design criterion alongside capacity, reach, and cost, reflected in every equipment selection decision, network architecture choice, and operational procedure. The optical transport network is uniquely positioned to enable a more sustainable digital future, provided the industry continues to invest in and deploy the technologies that make every picojoule count.

[1] ITU-T Recommendation L.1450 — Methodologies for the assessment of the environmental impact of the information and communication technology sector.

[2] Ericsson Mobility Report — Sustainability and ICT, ICT Sector Electricity Consumption and GHG Emissions.

[3] Malmodin, J. and Lunden, D. — ICT sector electricity consumption and greenhouse gas emissions, ScienceDirect.

[4] OIF (Optical Internetworking Forum) — Co-Packaged Optics Implementation Agreement.

[5] ITU-T Recommendation G.698.2 — Amplified multichannel dense wavelength division multiplexing applications with single channel optical interfaces.

[6] IEEE 802.3 — Ethernet Working Group, 800G and 1.6T task forces.

[7] Morea, A. et al. — Data-rate adaptation for night-time energy savings in core networks, J. Lightwave Technology.

[8] Dong, P. — Silicon photonic integration for coherent transceivers, Chapter 13, Digital Signal Processing in High-Speed Optical Fiber Communication.

[9] Sanjay Yadav, "Optical Network Communications: An Engineer's Perspective" — Bridge the Gap Between Theory and Practice in Optical Networking.

Developed by MapYourTech Team

For educational purposes in Optical Networking Communications Technologies

Note: This guide is based on industry standards, best practices, and real-world implementation experiences. Specific implementations may vary based on equipment vendors, network topology, and regulatory requirements. Always consult with qualified network engineers and follow vendor documentation for actual deployments.

Feedback Welcome: If you have any suggestions, corrections, or improvements to propose, please feel free to write to us at [email protected]

Optical Networking Engineer & Architect • Founder, MapYourTech

Optical networking engineer with nearly two decades of experience across DWDM, OTN, coherent optics, submarine systems, and cloud infrastructure. Founder of MapYourTech. Read full bio →

Follow on LinkedInRelated Articles on MapYourTech