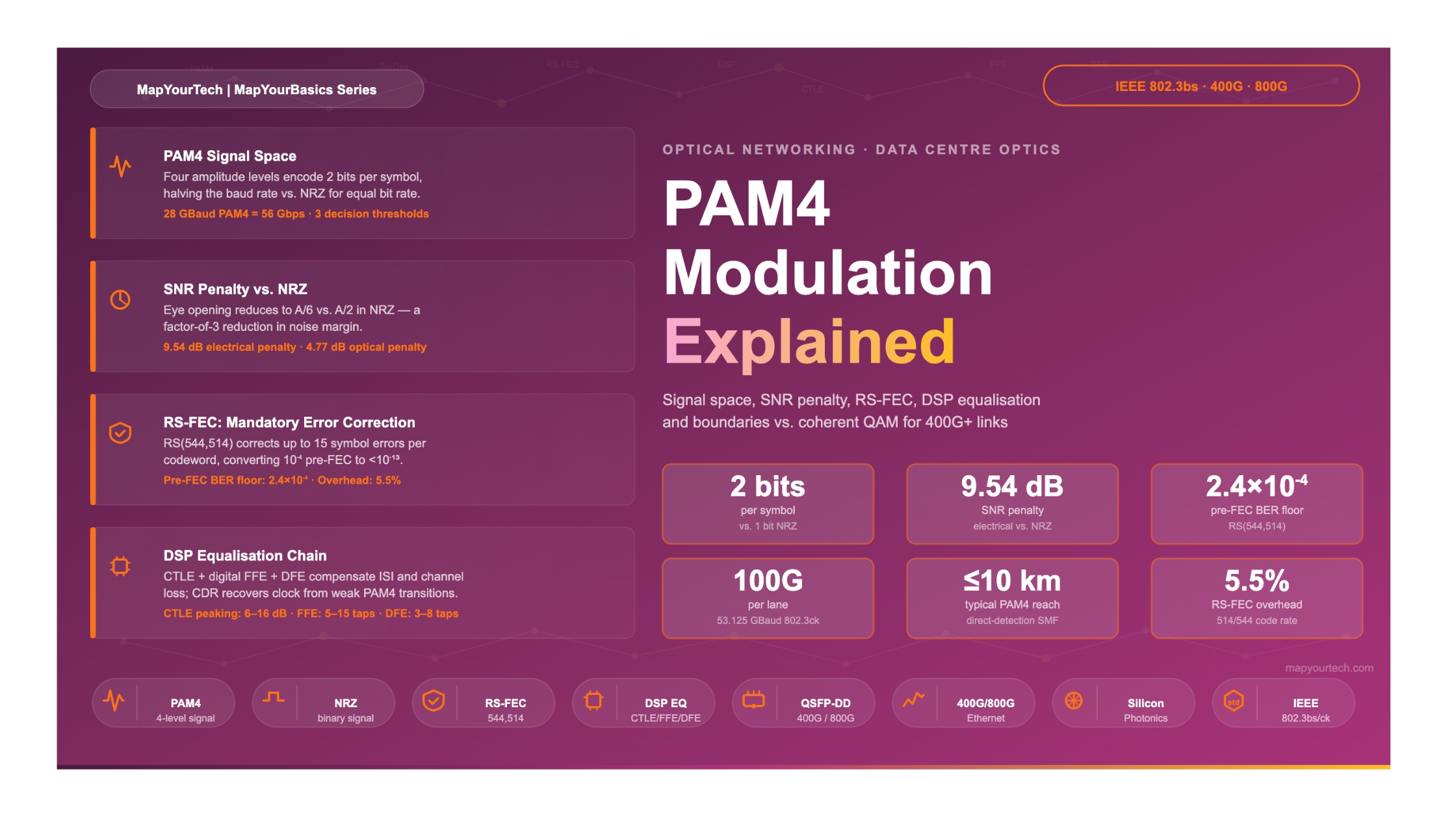

PAM4 Modulation for High-Speed Optical Interconnects

Operating Principle, OSNR Sensitivity, DSP Requirements, and the Boundary Between PAM4 and Coherent QAM in Modern Data Centre Networks

Contents

Introduction & Background

The relentless growth of data centre traffic, driven by cloud computing, artificial intelligence workloads, and high-performance computing, has steadily eroded the headroom of conventional binary optical signalling. For three decades, non-return-to-zero (NRZ) modulation — representing one bit per transmitted symbol — was sufficient to carry each successive generation of Ethernet from 1 Gbps through to 25 Gbps per lane. Beyond that threshold, a different approach was needed: one that could double the information carried in each symbol period without doubling the electrical bandwidth, which would otherwise collide with the physical limits of copper traces, connectors, and photodetectors.

Pulse Amplitude Modulation with four levels (PAM4) provides exactly that capability. By encoding two bits into each symbol using four distinct amplitude levels, PAM4 delivers twice the bit rate of NRZ for a given baud rate (symbol rate). A serialiser-deserialiser (SerDes) lane operating at 28 GBaud carries 28 Gbps with NRZ but 56 Gbps with PAM4. At 53.125 GBaud — the lane rate used in IEEE 802.3ck for 100 Gbps per lane — PAM4 becomes indispensable for realising 400G, 800G, and 1.6 Tbps aggregate interfaces without impractical lane counts.

This advantage comes with a well-understood penalty: because four amplitude levels must coexist within the same voltage swing as two NRZ levels, the spacing between adjacent PAM4 levels is one-third of the NRZ eye opening. The resulting signal-to-noise ratio (SNR) degradation — approximately 9.5 dB for electrical signals and 4.7 dB for optical power — is the central engineering challenge of PAM4 deployment, and it drives the entire supporting technology ecosystem: Reed-Solomon forward error correction (RS-FEC), linear and decision-feedback equalisation, and careful optical link budgeting.

This article examines each of these elements in depth. It explains the PAM4 signal space from first principles, derives the SNR penalty with worked examples, describes the role of FEC in converting an inherently error-prone link into a reliable one, surveys DSP equalisation architectures, and maps the boundary between short-reach PAM4 and longer-reach coherent QAM systems. The goal is to provide a complete, technically accurate reference for engineers designing or evaluating 100G, 400G, and 800G optical interconnects.

Historical Evolution

To appreciate why PAM4 emerged when it did, it is necessary to trace the trajectory of Ethernet lane rates and the physical constraints that governed each generation.

2.1 The NRZ Era: 1G to 25G

From the introduction of 1000BASE-SX in 1998 through the standardisation of 25GBASE-SR in IEEE 802.3by (2016), NRZ was the universal choice for data centre optical links. Each generation simply doubled or quadrupled the symbol rate: 1.25 GBaud for Gigabit Ethernet, 10.3125 GBaud for 10G, 25.78125 GBaud for 25G. Channel insertion loss at these frequencies remained manageable on standard FR4 printed circuit boards and OM3/OM4 multimode fibre.

100G was first achieved by parallelisation — four lanes of 25G NRZ in 100GBASE-SR4 (IEEE 802.3bm, 2015) and 100GBASE-LR4 (IEEE 802.3ba, 2010). This approach was acceptable for the first wave of 100G adoption, but extending it to 400G would have required sixteen 25G lanes or eight 50G NRZ lanes. Sixteen-lane modules were briefly standardised in 400GBASE-SR16, but the physical bulk, connector complexity, and cost of 16-fibre ribbon assemblies made the approach impractical for pervasive data centre deployment.

Continue Reading This Article

Sign in with a free account to unlock the full article and access the complete MapYourTech knowledge base.

2.2 The Transition to PAM4: 2017 and Beyond

The IEEE 802.3bs standard, ratified in December 2017, formalised PAM4 as the physical layer coding for 200G and 400G Ethernet. It defined 400GBASE-DR4 (four lanes of 100G PAM4 over parallel SMF, 500 m reach) and 400GBASE-FR8 (eight lanes of 50G PAM4 via WDM on a single SMF pair, 2 km reach), among others. Crucially, 802.3bs mandated Reed-Solomon FEC — specifically RS(544,514) — recognising that the intrinsic SNR of a PAM4 channel could not deliver the 10-13 raw bit error rate that NRZ links had historically achieved without assistance.

The OIF-CEI-56G-PAM4 specification from the Optical Internetworking Forum simultaneously defined the electrical interface for 56 Gbps PAM4 SerDes, covering medium-reach (MR) chip-to-chip and long-reach (LR) backplane applications. Together with 802.3bs, these two standards established PAM4 as the default modulation for all 400G+ electrical and direct-detection optical interfaces.

By 2022, IEEE 802.3ck had extended the principle to 100 Gbps per lane using 53.125 GBaud PAM4, enabling single-lane 100G transceivers and 800G modules with eight electrical lanes. PAM4 also entered PCIe 6.0 (2022), demonstrating that multi-level electrical signalling had moved far beyond optics into the processor interconnect domain.

Figure 1 — Ethernet lane rate milestones and the shift from NRZ to PAM4 modulation. The transition point in 2017 (IEEE 802.3bs) marks the crossover from binary to multi-level optical signalling at 56 Gbps and above.

The PAM4 Signal Space

3.1 Symbol Encoding and Constellation

In NRZ (PAM2) signalling, each clock period carries one bit: a logical "0" maps to the low amplitude level and a logical "1" maps to the high level. The decision boundary is placed midway between the two levels; noise must shift the amplitude past this single threshold to cause an error.

PAM4 extends this scheme to four amplitude levels — commonly labelled S0, S1, S2, and S3 in ascending order — each encoding a two-bit symbol (dibit). The standard Gray coding maps these as follows: S0 → 00, S1 → 01, S2 → 11, S3 → 10. Gray coding is critical because it ensures that an error that misidentifies an adjacent level (the most probable type of error) produces only a single bit error rather than two, which improves the raw bit-error-to-symbol-error relationship.

Figure 2 — NRZ (PAM2) versus PAM4 signal structure. The NRZ eye spans the full amplitude A; each of the three PAM4 eyes spans only A/3, reducing SNR margin significantly and mandating FEC for reliable operation.

3.2 Why the Nyquist Frequency Matters

The Nyquist frequency of a serial link is half the symbol rate. An NRZ signal at 56 Gbps requires a Nyquist frequency of 28 GHz. A PAM4 signal carrying the same 56 Gbps requires only 28 GBaud — half the symbol rate — reducing the Nyquist frequency to 14 GHz. This 2× reduction in required channel bandwidth is the fundamental engineering motivation for PAM4. At 14 GHz, channel insertion loss on a standard IEEE 802.3 compliant backplane is roughly 33 dB. At 28 GHz (NRZ for 56G), the same board shows approximately 62 dB insertion loss — nearly twice as much, and far harder to equalise.

The lower Nyquist frequency also reduces inter-symbol interference (ISI) from frequency-dependent channel loss, simplifies the design of continuous-time linear equalisers (CTLE) and feed-forward equalisers (FFE), and eases the thermal constraints on transmitter pre-emphasis circuits. All of these factors combine to make PAM4 a more attractive option for 56 Gbps and above, despite its SNR penalty.

PAM4 trades SNR margin for channel bandwidth. The half-baud-rate advantage reduces channel insertion loss by 11+ dB on typical backplanes — a much larger saving than the ~9.5 dB SNR cost. FEC bridges the remaining noise margin gap.

SNR Penalty Versus NRZ

4.1 Derivation from First Principles

Consider a signal occupying a voltage swing of A (peak-to-peak). In NRZ, the two levels are separated by A, and the single decision threshold sits at A/2. The minimum noise amplitude needed to cause an error is A/2.

In PAM4, the same swing A is divided among four equally spaced levels. The inter-level spacing becomes A/3, and there are three decision boundaries, each placed at the midpoint between adjacent levels (at A/6, 3A/6, and 5A/6 relative to the lowest level). The minimum noise required to cause an error is now A/6 — one-third of the NRZ case.

SNR_penalty = 20 × log10( eye_NRZ / eye_PAM4 ) = 20 × log10( A/2 / A/6 ) = 20 × log10( 3 ) = ≈ 9.54 dB (electrical voltage ratio)

For optical power (detected photocurrent ∝ optical power, SNR ∝ power²): SNR_penalty_optical = 10 × log10( 3 ) = ≈ 4.77 dB (optical power ratio)

- eye_NRZ — NRZ eye opening = A/2 (half the full voltage swing)

- eye_PAM4 — PAM4 eye opening = A/6 (one-third of NRZ eye)

- A — total signal voltage (or optical power) swing

- Result — PAM4 requires ~9.5 dB more electrical SNR (or ~4.8 dB more optical power SNR) to achieve the same BER as NRZ at the same noise level

The 9.54 dB figure applies to voltage-domain measurements (oscilloscope, electrical BER testers). Optical power is a linear quantity; squared in the detector, so the optical SNR penalty is 10 log₁₀(3) ≈ 4.77 dB. Tektronix confirms a drop in SNR of a factor of three (9.5 dB for electrical voltage, 4.7 dB for optical power) for PAM4 versus NRZ.

4.2 Bit Error Rate Implications

For an NRZ channel operating with additive white Gaussian noise, the bit error rate (BER) as a function of SNR per bit (Eb/N0) follows the complementary error function. PAM4 with Gray coding has a more complex BER expression because symbol errors in the inner eyes (S1–S2 and S2–S3) produce single bit errors, while symbol errors at the outer eyes (S0–S1 and S3–S2... S2–S3) can also produce single bit errors due to Gray encoding. The approximate BER for equally spaced PAM4 levels with Gray coding is:

BER_PAM4 ≈ 3/2 × erfc( d_min / (2σ × sqrt(2)) ) where: d_min = A/3 (minimum inter-level spacing) σ = RMS noise standard deviation erfc = complementary error function

Worked Example: If a NRZ link achieves BER = 10-12 with an SNR of X dB, the same channel with PAM4 at the same baud rate achieves: BER ≈ 10-4 to 10-3 (due to ~9.5 dB SNR loss) This motivates the use of RS-FEC with a pre-FEC BER floor ≤ 2.4×10-4.

4.3 The Three-Eye Diagram

NRZ signal quality is assessed with a single eye diagram — one opening between the two levels. PAM4 produces three superimposed eye openings (upper, middle, lower), one for each adjacent pair of levels. All three eyes must simultaneously meet height and width specifications. The middle eye is the most sensitive: random noise and intersymbol interference contribute from both inner-eye transitions, making it statistically the worst eye in practice.

IEEE 802.3bs defines the eye mask specifications for each of the three eyes, along with metrics such as eye height (EH), eye width (EW), and the signal level non-uniformity (SLEVnoiseX) that accounts for unequal spacing between levels. Level non-uniformity degrades the effective BER of the worst eye and must be controlled by the transmitter linearity specification.

Forward Error Correction

5.1 Why FEC is Mandatory

NRZ links at 25G and 100G (in 100GBASE-LR4 and -SR4) operated at raw BERs of 10-12 or better, and many applications tolerated this without any FEC. The raw BER of a well-designed PAM4 link — even with good equalisation — is typically in the range of 10-5 to 10-3, several orders of magnitude worse. Ethernet protocols require a post-FEC BER of at most 10-13 at the MAC layer. The gap between pre-FEC PAM4 BER and this target is bridged exclusively by FEC.

IEEE 802.3bs made Reed-Solomon FEC mandatory for all PAM4 optical PMDs. This was a departure from earlier Ethernet standards, where FEC was optional or absent. The standard specifies RS(544,514) as the baseline FEC for 400G PAM4 links.

5.2 Reed-Solomon RS(544,514) Operation

Reed-Solomon (RS) codes are a class of systematic block codes operating over the Galois field GF(2m). The notation RS(n, k) means n symbols per codeword, of which k are data symbols and (n − k) are parity symbols. Each symbol is m bits wide. For RS(544,514) used in IEEE 802.3bs:

n = 544 symbols per codeword k = 514 data symbols per codeword 2t = n - k = 30 parity symbols t = 15 symbol errors correctable per codeword m = 10 bits per symbol (GF(210)) Code rate = 514/544 ≈ 0.9449 (5.5% overhead) Pre-FEC BER floor (target) ≤ 2.4 × 10-4 Post-FEC BER (target) ≤ 10-13 to 10-15

The FEC decoder corrects up to 15 symbol errors per 544-symbol codeword. A symbol error results from one or more bit errors within the 10-bit symbol. The RS code is therefore highly effective against burst errors and moderately effective against random errors. When the pre-FEC BER exceeds 2.4×10-4, the number of symbol errors per codeword starts to exceed 15 too frequently, and the post-FEC BER begins to rise steeply — a phenomenon called FEC cliff. Staying well below the pre-FEC BER floor is the primary goal of the optical and electrical link design.

5.3 Latency Considerations

RS-FEC introduces a deterministic latency increment. The FEC encoder must accumulate a full codeword before transmission, and the decoder must receive and process the complete codeword before outputting corrected data. For RS(544,514) at 400G, the latency contribution is approximately 30–100 nanoseconds depending on implementation. While negligible for most storage and cloud applications, this becomes relevant in high-frequency trading environments and distributed storage systems where end-to-end latency budgets are stringent.

| FEC Type | Standard | Pre-FEC BER Target | Overhead | Latency | Use Case |

|---|---|---|---|---|---|

| None | 25G NRZ | <10-12 | 0% | Zero | Short-reach NRZ links |

| KR4 (Clause 91) | 100GBASE-KR4 | <6×10-6 | 2.56% | ~100 ns | 100G backplane NRZ |

| RS(544,514) | IEEE 802.3bs | ≤2.4×10-4 | 5.5% | ~100 ns | 400G+ PAM4 optical |

| RS(272,258) | IEEE 802.3cd | ≤2.4×10-4 | 5.5% | ~50 ns | 200G/50G PAM4 |

| SD-FEC (LDPC) | Coherent (OIF) | ~10-2 | 15–25% | >1 μs | Long-haul coherent |

Table 1 — FEC types, their standards, pre-FEC BER requirements, overhead, and typical latency. RS(544,514) is mandatory for 400G PAM4 under IEEE 802.3bs.

DSP Equalisation Requirements

Even with RS-FEC handling residual errors, the raw SNR reaching the FEC decoder must be kept above the 2.4×10-4 BER threshold. Achieving this in a real channel — with frequency-dependent loss, reflections, crosstalk, and nonlinear transmitter behaviour — is the job of the equalisation subsystem. PAM4 links require more sophisticated equalisation than NRZ because three threshold comparisons must each achieve adequate eye opening simultaneously.

6.1 Continuous-Time Linear Equaliser (CTLE)

The CTLE is an analogue filter, typically implemented as a source-degenerated differential pair or a differential cascade, that applies a frequency-dependent gain profile to the received signal. Its transfer function is shaped to boost high-frequency components attenuated by the channel, partially restoring the eye opening before sampling. The CTLE is the first stage of equalisation and operates at full symbol rate in the analogue domain.

For PAM4 links, the CTLE must provide adequate gain at the Nyquist frequency (half the baud rate) while avoiding noise enhancement at frequencies beyond Nyquist. The gain-peaking characteristic is typically expressed in dB at the Nyquist frequency. IEEE 802.3bs defines the adapted CTLE response as part of the channel operating margin (COM) compliance metric.

6.2 Feed-Forward Equaliser (FFE)

The FFE is a transversal (FIR) filter applied either at the transmitter (TX FFE, also called TX pre-emphasis or pre-distortion) or at the receiver (RX FFE). It uses a set of N taps, each multiplying a delayed version of the signal by a coefficient, to cancel ISI from preceding symbol periods. The output is the weighted sum of N delayed samples:

y[n] = Σ c[k] × x[n-k] for k = 0 to N-1 where: y[n] — equalised output at sample time n c[k] — tap coefficient k (real-valued, adapted by LMS algorithm) x[n-k] — input sample at time n-k (delayed by k symbol periods) N — number of FFE taps (typically 5–15 for PAM4 receivers) Tap adaptation: c[k] = c[k] + μ × e[n] × x[n-k] where e[n] is the error signal and μ is the adaptation step size

TX pre-emphasis applies the FFE before the signal enters the channel, so it introduces intentional waveform distortion at the transmitter that partially cancels the channel's distortion. This approach is particularly useful when the channel is well characterised (as in backplane applications). RX FFE adapts to the actual received signal and is more flexible for unknown or time-varying channels.

6.3 Decision-Feedback Equaliser (DFE)

The DFE is a nonlinear equaliser that uses previously decoded symbols to cancel post-cursor ISI — the residual interference from symbols that arrived before the current sample. Once a symbol decision has been made, the known symbol value multiplied by the DFE tap coefficient is subtracted from the input signal before the next decision.

v[n] = y[n] - Σ d[j] × â[n-j] for j = 1 to M where: v[n] — DFE output (ISI-cancelled signal) y[n] — input to DFE (FFE output or CTLE output) d[j] — DFE feedback tap coefficient j â[n-j]— decision on symbol at time n-j (quantised to nearest PAM4 level) M — number of DFE taps (typically 3–8)

The DFE advantage over a linear equaliser is that it does not enhance noise: feedback is from clean decoded symbols, not from the noisy received signal. Its limitation is error propagation — a wrong decision in â[n-j] injects a wrong cancellation signal into subsequent samples, potentially creating a chain of errors. This makes the DFE sensitive to bursts of errors and explains why FEC is applied after the DFE rather than before.

6.4 Clock and Data Recovery (CDR)

Recovering a clean clock from a PAM4 signal is harder than from NRZ. In NRZ, every transition between "0" and "1" crosses the midpoint with full amplitude swing — providing a strong timing reference. In PAM4, only 1/6 of transitions cross between S0 and S3 (the outer levels with full swing). The remaining 5/6 of transitions have smaller amplitude swings of either 1/3 or 2/3 of full swing, producing weaker timing information. The CDR must track phase from these weaker transitions, requiring more sophisticated phase-locked loop (PLL) design or DSP-based digital CDR algorithms.

Figure 4 — PAM4 receiver DSP chain from optical input to decoded bit stream. The analogue stage (CTLE) is followed by ADC, digital FFE, DFE, three-threshold slicer, and RS-FEC. The DFE feedback loop operates one symbol period after the slicer decision.

Optical Implementation

7.1 Light Sources and Modulators

PAM4 optical transmitters must generate four distinct, well-separated optical power levels from a continuous-wave (CW) laser source. Two dominant architectures exist:

Direct modulation of distributed feedback (DFB) lasers: At rates up to approximately 28 GBaud, DFB lasers can be directly modulated with a four-level electrical drive signal. Direct modulation is cost-effective but introduces chirp (wavelength variation correlated with intensity change), which causes dispersion penalty on single-mode fibre links. Chirp tolerance must be evaluated against the dispersion budget of the target reach.

Electro-absorption modulated lasers (EML) and external Mach-Zehnder modulators: For 50 GBaud and above (100G per lane), chirp-free external modulation is preferred. EMLs integrate the DFB laser and electro-absorption modulator in a single device, offering a compact solution with low chirp and bandwidth sufficient for 53.125 GBaud PAM4. Silicon photonics Mach-Zehnder modulators (SiPh MZM) provide even wider bandwidth and are increasingly used in 400G and 800G transceivers.

7.2 Photodetectors and Receiver Optics

The photodetector in a PAM4 receiver must have sufficient bandwidth, responsivity, and linearity to distinguish all four amplitude levels. A 28 GBaud PAM4 receiver requires a photodetector bandwidth of at least 20 GHz, while a 53.125 GBaud receiver requires approximately 35–40 GHz bandwidth. InGaAs positive-intrinsic-negative (PIN) photodiodes are standard for high-linearity direct-detection applications. Avalanche photodiodes (APDs) offer higher responsivity (gain) but at the cost of excess noise factor, which degrades the effective SNR for PAM4 compared to NRZ to a greater degree.

7.3 OSNR Budget for PAM4 Links

In directly detected PAM4 systems — unlike coherent systems — there is no optical local oscillator, and optical signal-to-noise ratio (OSNR) is not the primary figure of merit. The performance metric is optical modulation amplitude (OMA) and its relationship to the receiver sensitivity. However, for PAM4 links using wavelength-division multiplexed (WDM) approaches — such as 400GBASE-LR8 using eight wavelengths on DWDM or CWDM4 grids — the OSNR of each WDM channel must be maintained above the minimum required for the photodetector and equaliser chain to achieve the target pre-FEC BER.

In single-wavelength PAM4 modules (e.g., 400GBASE-DR4 using four parallel SMF fibres), OSNR is not the limiting factor — optical power budget (launch power minus path loss versus receiver sensitivity) determines reach. In WDM PAM4 systems, OSNR must be calculated per-channel including amplifier ASE noise. The PAM4 penalty means more OSNR is consumed per channel than an equivalent coherent system at the same bit rate, which is one reason WDM PAM4 is limited to relatively short reaches (2–10 km).

7.4 Silicon Photonics and Co-Packaged Optics

Silicon photonics (SiPh) platforms enable monolithic integration of PAM4 modulators, photodetectors, and driver electronics using standard CMOS fabrication processes. As of 2025, SiPh-based 400G transceivers offer 10–15% lower power consumption compared to equivalent InP-based designs, while maintaining the full bandwidth required for 53.125 GBaud operation. Co-packaged optics (CPO) — where the optical transceiver is integrated into the same package as the switch ASIC — eliminates the 112Gbps SerDes copper trace between switch and pluggable module, resolving the electrical signal integrity bottleneck for 1.6 Tbps and higher switch bandwidths.

PAM4 vs. Coherent QAM — Application Boundaries

PAM4 and coherent QAM represent two fundamentally different optical technologies that target complementary network segments. Understanding where each is appropriate prevents both over-engineering short links with expensive coherent hardware and under-engineering longer links that PAM4 cannot adequately serve.

8.1 Detection Philosophy

PAM4 uses direct detection: the optical power is converted directly to photocurrent by the photodetector, discarding phase information. The modulated quantity is optical intensity (power). This is simple, low-cost, and sufficient for short reaches where dispersion and nonlinearity are negligible.

Coherent QAM uses coherent detection: the received signal is mixed with a local oscillator laser in a 90° optical hybrid, and both in-phase (I) and quadrature (Q) components of the electric field are measured on two pairs of balanced photodetectors. This recovers both amplitude and phase, enabling 2D modulation formats such as DP-QPSK (2 bits/symbol per polarisation), DP-16QAM (4 bits/symbol per polarisation), and DP-64QAM (6 bits/symbol per polarisation). The DSP in a coherent receiver can digitally compensate for chromatic dispersion (CD) and polarisation mode dispersion (PMD) accumulated over thousands of kilometres.

Figure 5 — PAM4 direct-detection and coherent QAM application zones as a function of reach and capacity. The two technologies overlap in the 10–80 km range where coherent-lite and ZR-lite options compete with WDM PAM4.

8.2 Quantitative Comparison

| Parameter | PAM4 (Direct Detection) | DP-16QAM (Coherent) |

|---|---|---|

| Bits per symbol | 2 (single polarisation) | 8 (4 bits × 2 polarisations) |

| Modulation dimensions | Amplitude only (1D) | Amplitude + Phase + Polarisation (4D) |

| Detection method | Direct (photodiode, no LO) | Coherent (90° hybrid + LO laser) |

| CD compensation | No (dispersion limits reach) | Yes (digital, unlimited reach) |

| PMD compensation | No | Yes (digital MIMO) |

| OSNR requirement (400G) | ~20–22 dB (typical) | ~21–23 dB (DP-16QAM, 400G) |

| Typical reach | 100 m – 10 km | 80 km – 3,000+ km |

| Transceiver cost | Low–medium ($300–$1,000) | High ($2,000–$10,000+) |

| Power consumption | 5–15 W | 15–25 W |

| DSP complexity | Low–medium (CTLE/FFE/DFE) | High (CD comp, MIMO, carrier recovery) |

| Form factor | QSFP-DD, OSFP, SFP-DD | QSFP-DD, OSFP, CFP2-DCO |

| FEC | RS(544,514) — 5.5% overhead | SD-FEC (LDPC) — 15–25% overhead |

| Primary use case | Data centre intra- and inter-rack | DCI, metro, regional, long-haul |

Table 2 — Quantitative comparison of PAM4 direct-detection and coherent DP-16QAM. Values shown are typical for 400G-class products as of 2025.

8.3 The Decision Framework

The choice between PAM4 and coherent comes down to three primary factors: reach, cost per bit, and operational flexibility. For reaches below 10 km — covering the vast majority of intra-data-centre links — PAM4 offers the superior cost-per-bit ratio by eliminating the local oscillator laser, 90° hybrid coupler, four-balanced-photodetector array, and the accompanying coherent DSP ASIC. The lower component count also reduces power consumption and module footprint.

Once reach exceeds 10–20 km, chromatic dispersion begins to close the PAM4 eye diagram. At 1310 nm (where 400GBASE-DR4 and -LR4 operate), standard SMF has approximately 3.5–5 ps/nm/km of dispersion. A 53.125 GBaud PAM4 signal has a symbol period of ~18.8 ps. Over 10 km, dispersion accumulates to 35–50 ps/nm, causing adjacent PAM4 symbols to overlap and reducing the eye opening below the FEC pre-BER floor. This physical constraint — not cost — is the fundamental limit of PAM4 reach on standard SMF.

Performance, Standards, and Link Budgets

9.1 Key IEEE Standards for PAM4

| PMD | Standard | Lanes | Rate/Lane | Baud Rate | Medium | Reach |

|---|---|---|---|---|---|---|

| 400GBASE-SR8 | 802.3cm | 8 | 50G | 26.5625 GBaud | OM4 MMF | 100 m |

| 400GBASE-DR4 | 802.3bs | 4 | 100G | 53.125 GBaud | SMF parallel | 500 m |

| 400GBASE-FR4 | 802.3bs | 4 WDM | 100G | 53.125 GBaud | SMF CWDM | 2 km |

| 400GBASE-LR4 | 802.3bs | 4 WDM | 100G | 53.125 GBaud | SMF DWDM/CWDM | 10 km |

| 400GBASE-LR8 | 802.3bs | 8 WDM | 50G | 26.5625 GBaud | SMF WDM | 10 km |

| 800GBASE-DR8 | 802.3ck | 8 | 100G | 53.125 GBaud | SMF parallel | 500 m |

| 100GBASE-DR | 802.3cu | 1 | 100G | 53.125 GBaud | SMF | 500 m |

Table 3 — Key PAM4 optical PMDs from IEEE 802.3. Baud rates shown are the raw symbol rate before RS-FEC overhead.

9.2 Channel Operating Margin (COM)

IEEE 802.3 uses Channel Operating Margin (COM) as the primary compliance metric for PAM4 electrical interfaces. COM is defined in IEEE 802.3 Annex 93A and expressed in decibels. A positive COM value indicates a compliant channel; a negative COM indicates the channel will not reliably support the target data rate. The COM computation accounts for channel insertion loss, return loss, crosstalk (NEXT and FEXT), transmitter noise, and the equalisation capability (CTLE + FFE + DFE) of the receiver model.

COM = 20 × log10( A_s / A_n ) [dB] where: A_s — signal component amplitude at decision point (after equalisation) A_n — noise + ISI + crosstalk amplitude at decision point Compliance threshold: COM ≥ 0 dB Typical design target: COM ≥ 3–6 dB (for yield margin)

Practical Applications and Case Studies

10.1 Hyperscale Data Centre Spine-Leaf Fabric

A typical modern hyperscale data centre deploys a Clos (spine-leaf) fabric with 400G uplinks between leaf and spine switches. Each 400G port uses a 400GBASE-DR4 transceiver operating four lanes of 100G PAM4 at 53.125 GBaud over parallel SMF, covering the 2–100 m distances typical of top-of-rack to end-of-row to aggregate switch hops. The RS(544,514) FEC in each transceiver ensures that even when a lane encounters crosstalk from adjacent fibres in a ribbon cable, the post-FEC BER remains below 10-13.

A 128-port 400G leaf switch requires 128 × 4 = 512 PAM4 SerDes lanes on the switch ASIC. At 53.125 GBaud per lane, the total aggregate switching capacity is 128 × 400 Gbps = 51.2 Tbps. The ability of PAM4 to deliver 400G within the QSFP-DD pluggable form factor — at under 12 W per transceiver and costs in the $300–$600 range for 500 m reach — has been the primary driver of this deployment model since 2020.

10.2 400GBASE-LR8 for Inter-Building Links

When two buildings in a campus or metro area must be connected at 400G over distances of 2–10 km, 400GBASE-LR8 uses WDM to carry eight 50G PAM4 lanes over a single SMF pair. The eight wavelengths are positioned on a CWDM-style grid, with approximately 800 GHz spacing. Each lane uses 26.5625 GBaud PAM4 to achieve 50 Gbps. The wider channel spacing reduces wavelength-dependent penalty and eliminates the need for thermal wavelength control, keeping transceiver cost lower than a DWDM alternative.

The dispersion challenge is manageable at 26.5625 GBaud: the symbol period is ~37.6 ps, and dispersion of 35 ps/nm over 10 km on standard SMF (at 1310 nm) represents less than one symbol period of broadening, keeping the PAM4 eyes open with adequate margin after CTLE and FFE equalisation.

10.3 PAM4 in 5G Fronthaul

5G fronthaul networks — connecting baseband units (BBUs) or distributed units (DUs) to remote radio units (RRUs) — require high capacity over fibre spans of typically 10–30 km. Bi-directional 50G PAM4 transceivers (BiDi, using single fibre with two wavelengths per fibre) are deployed for midhaul links at 10 km reach, providing cost-effective 50G capacity within the power and form factor constraints of outdoor cabinets. The use of PAM4 at 50G per fibre replaces two 25G NRZ fibres, halving the fibre consumption without coherent complexity.

10.4 Worked Link Budget Example

Given: Target rate: 100 Gbps per lane (4 lanes = 400G aggregate) Baud rate: 53.125 GBaud (PAM4, 2 bits/symbol) Launch power (OMA): 0.0 dBm (typ. min per 802.3bs) Receiver sensitivity:-7.5 dBm (OMA, typ. at pre-FEC BER = 2.4×10-4) Connector loss: 2 × 0.5 dB = 1.0 dB Fibre attenuation: 0.4 dB/km × 0.5 km = 0.2 dB (at 1310 nm) Dispersion penalty: 0.5 dB (SMF at 1310 nm over 500 m) Total channel loss = 1.0 + 0.2 + 0.5 = 1.7 dB Received power (OMA) = 0.0 dBm - 1.7 dB = -1.7 dBm Margin = Received - Sensitivity = -1.7 - (-7.5) = +5.8 dB Result: 5.8 dB positive margin — compliant link Note: RS(544,514) FEC converts pre-FEC BER ≤ 2.4×10-4 to post-FEC BER <10-13

Section 10 Key Points

Challenges and Solutions

11.1 Level Non-Uniformity and Transmitter Linearity

If the four amplitude levels of a PAM4 transmitter are not equally spaced, the three eye openings will have different heights. The smallest eye sets the BER floor of the link. Level non-uniformity arises from laser modulation nonlinearity, DAC/driver nonlinearity, and optical power-to-current conversion nonlinearity in the photodetector. IEEE 802.3bs limits the allowed level mismatch through specifications on signal level non-uniformity ratio (SLNR) and requires the transmitter to meet OMA specifications for each individual eye.

Pre-distortion at the transmitter — applying a nonlinear correction to the drive signal based on a characterised model of the transmitter nonlinearity — is the primary mitigation. Modern PAM4 DSP ASICs include lookup tables or polynomial correction engines that map the desired four-level sequence to the actual drive voltages needed to produce equal optical levels after propagation through the nonlinear transmitter.

11.2 Crosstalk in Multi-Lane PAM4 Assemblies

High-density 400G and 800G modules integrate multiple PAM4 lanes in close proximity on a single PCB or within a single module housing. Near-end crosstalk (NEXT) and far-end crosstalk (FEXT) between adjacent SerDes lanes degrade the SNR of each individual lane. IEEE 802.3 standards quantify the crosstalk tolerance through the COM metric and set limits on the aggressor channel NEXT/FEXT levels.

Mitigation strategies include electromagnetic shielding between transmit and receive paths, controlled differential impedance on PCB traces, and careful package-level routing. The COM calculation in IEEE 802.3 Annex 93A explicitly includes crosstalk in the noise budget, ensuring that a COM-compliant channel design accounts for realistic multi-lane crosstalk environments.

11.3 Error Propagation in DFE

As discussed in Section 6.3, DFE error propagation can degrade link performance under burst noise conditions. When a burst of errors (e.g., from a reflection or a momentary dusty optical connector) occurs, the DFE may propagate errors for several symbol periods beyond the burst duration, inflating the pre-FEC BER above the RS-FEC threshold. This is mitigated by limiting the number of DFE taps, using a DFE with a leaky integrator that slowly decays erroneous feedback contributions, and ensuring that the RS-FEC codeword interleaver distributes burst errors across multiple codewords so no single codeword exceeds the 15-symbol correction capability.

11.4 Power Consumption

PAM4 receivers consume more power than NRZ receivers at equivalent bit rates due to the higher-resolution ADC needed (typically 6–7 effective bits for PAM4 versus 1–2 bits for NRZ), the more complex equalisation (3–5 FFE/DFE taps instead of 1–2), and the RS-FEC logic. A 400G PAM4 transceiver typically dissipates 12–15 W, compared to 3–5 W for a 100G NRZ module at equivalent form factor. Silicon photonics and advanced CMOS DSP processes (below 7 nm) are the primary vectors for reducing this power gap.

Future Directions

PAM4 at 53.125 GBaud per lane defines the 100G-per-lane generation standardised in IEEE 802.3ck (2023). The next generation — 200G per lane — is under development in IEEE 802.3df and requires PAM4 operation at approximately 106.25 GBaud. At this symbol rate, the Nyquist frequency exceeds 50 GHz, which pushes the boundaries of InP and SiPh electro-optic bandwidth and the performance of ADCs and DACs in the SerDes. Whether 200G-per-lane systems will use PAM4 or will transition to a higher-order scheme such as PAM8 (3 bits/symbol, 3-level eye hierarchy) remains under active investigation; the SNR penalty of PAM8 relative to PAM4 is a further ~4.8 dB, likely requiring even more aggressive FEC or more capable optical components.

Co-packaged optics (CPO) will extend the reach of PAM4 by eliminating the high-loss copper SerDes lane between the ASIC and pluggable module. With CPO, the PAM4 modulator is driven directly from the ASIC die through micro-bump connections, reducing the electrical channel loss from ~20 dB (for a 100G lane over 10 cm of PCB trace at 53 GHz) to essentially zero. This relaxes the equalisation requirement and permits operation at higher baud rates with less DSP power.

Beyond CPO, optical electrical integrated circuits (OEICs) and photonic integrated circuits (PICs) will further compress the size and power of PAM4 transceivers. The goal for the 1.6 Tbps generation is a total module power envelope below 30 W — roughly 1.9 W per 100G — enabled by SiPh modulators, monolithically integrated driver electronics, and advanced FEC at 3 nm CMOS.

800G-ZR, using DP-64QAM coherent modulation, is emerging as a 80 km DCI solution that competes with multi-span WDM PAM4 systems. At the same time, 800G PAM4 (eight lanes of 100G PAM4) targets 500 m to 2 km reaches where coherent cost and power are unjustifiable. The technology boundary is shifting, not disappearing.

Glossary and References

References

Developed by MapYourTech Team

For educational purposes in Optical Networking Communications Technologies

Note: This article is based on industry standards, best practices, and real-world implementation experience. Specific values may vary by implementation, vendor, and deployment environment. Always consult qualified engineers and vendor documentation for actual network design.

Feedback Welcome: Suggestions, corrections, or improvements — write to [email protected]

Optical Communications & Network Automation Expert | Author of 3 Books for Optical Engineers | Founder, MapYourTech

Optical networking engineer with nearly two decades of experience across DWDM, OTN, coherent optics, submarine systems, and cloud infrastructure. Founder of MapYourTech. Read full bio →

Follow on LinkedInRelated Articles on MapYourTech